UNIVAC®

1218

MILITARY

COMPUTER

PROGRAMMERS REFERENCE MANUAL

### UNIVAC 1218

# UNIVAC 1218

November, 1969

CHANGE 2

To: All holders of the 1218 Programmers Reference Manual, PX 2910.

From: Advanced Programming Department

Insert the changes as follows:

(with 33 enclosures)

- 1. Title page: Remove and replace with new title page attached.

- 2. Remove page iii and replace with new page iii attached.

- 3. Remove Table of Contents pages ix/x thru xxv and replace with new pages ix/x thru xxvii attached.

- 4. Remove page II-D-23/II-D-24 and replace with new page II-D-23/II-D-24 attached.

- 5. Following Section II-F insert new tab, "9200/9300 Subsystem," and new pages II-G-1/11-G-2 thru II-G-39.

## PROGRAMMERS REFERENCE MANUAL FOR UNIVAC 1218 COMPUTER

PX 2910

**REVISION C**

**CHANGE 2**

**NOVEMBER 1969**

#### CHANGE 2

#### CHANGE RECORD

| Change No.        | Date          | Reason for Change                                                                                               |

|-------------------|---------------|-----------------------------------------------------------------------------------------------------------------|

| Rev C             | August 1968   | Retyped and extensively revised entire manual.                                                                  |

| Rev C<br>Change 1 | July 1969     | Updated and revised manual. Deleted section on 1469 High-Speed Printer.                                         |

| Change 2          | November 1969 | Added Section II-G which describes the use of the 9200/9300 Computer as a peripheral device. Minor corrections. |

|                   |               |                                                                                                                 |

|                   |               |                                                                                                                 |

|                   |               |                                                                                                                 |

|                   |               |                                                                                                                 |

|                   |               |                                                                                                                 |

|                   |               |                                                                                                                 |

|                   |               |                                                                                                                 |

|                   |               |                                                                                                                 |

|                   |               |                                                                                                                 |

#### LIST OF EFFECTIVE PAGES

| Page No.              | Change in Effect | Page No.               | Change in Effect |

|-----------------------|------------------|------------------------|------------------|

| Title Page            | Rev C, Change 2  | III-C-27               | Rev C, Change 1  |

| ii thru iii           | Rev C, Change 2  | III-C-28 thru III-C-30 | Rev C            |

| V                     | Rev C, Change 1  | III-C-31 thru III-C-42 | Rev C, Change 1  |

| Letter                | Rev C            | IV-1                   | Rev C, Change 1  |

| ix                    | Rev C, Change 2  | IV-A-1 thru $IV-A-14$  | Rev C            |

| xv thru xxvii         | Rev C, Change 2  | IV-B-1 thru IV-B-25    | Rev C            |

| I-3                   | Rev C            | IV-B-26 thru IV-B-28   | Rev C, Change 1  |

| I-A-1 thru I-A-15     | Rev C            | IV <b>-</b> B-29       | Rev C            |

| I-B-1 thru I-B-46     | Rev C            | IV-B-30 thru IV-B-34   | Rev C, Change 1  |

| I-C-l thru I-C-17     | Rev C            | IV-B-35 thru IV-B-40   | Rev C            |

| II-]                  | Rev C            | IV-C-1 thru IV-C-6     | Rev C            |

| II-A-1 thru II-A-12   | Re <b>v</b> $C$  | IV-D-1                 | Rev C, Change 1  |

| II-B-1 thru II-B-8    | Rev C            | IV-D-2 thru IV-D-6     | Rev C            |

| II-C-1 thru II-C-7    | Rev C            | IV-D-7 thru IV-D-8     | Rev C, Change 1  |

| II-C-8                | Rev C, Change 1  | IV-D-9 thru IV-D-10    | Rev C            |

| II-C-9 thru II-C-23   | Rev C            | IV-E-1                 | Rev C, Change 1  |

| II-D-1 thru II-D-23   | Rev C            | IV-E-2                 | Rev C            |

| II-D-24               | Rev C, Change 2  | IV-E-3 thru IV-E-4     | Rev C, Change 1  |

| II-D-25 thru II-D-29  | Rev C            | IV-F-1                 | Rev C, Change 1  |

| II-E-1                | Rev C, Change 1  | IV-F-2 thru IV-F-11    | Rev C            |

| II-F-1 thru II-F-10   | Rev C            | IV- F-12 thru IV-F-14  | Rev C, Change 1  |

| II-F-11               | Rev C, Change 1  | V-1                    | Rev C            |

| II-G-1 thru II-G-39   | Rev C, Change 2  | V-A-1 thru V-A-16      | Rev C            |

| III-1 thru III-2      | Rev C            | V-B-1 thru V-B-2       | Rev C            |

| III-A-1 thru III-A-13 | Rev C            | V-C-1 thru $V-C-4$     | Rev C            |

| III-B-1 thru III-B-26 | Rev C            | A-l thru A-4           | Rev C            |

| III-C-1 thru III-C-26 | Rev C            | -                      | •                |

#### PREFACE

The UNIVAC 1218 System includes the UNIVAC R 1218 Military Computer, standard peripheral equipment, and a set of standard computer software. This manual was written to meet the needs and requirements of the programmer. It gives general information about the computer, peripheral equipment, and the standard software available with the computer. The principal software packages consists of:

- 1) Assemblers.

- 2) Operator service routines.

- 3) Programmer service subroutines.

Organizationally, the manual is comprised of five major sections, each of which has several parts. Section I contains general information concerning the computer hardware and functional capabilities of the computer. It gives the reader logical and functional characteristics of the instruction repertoire and describes the Input/Output (I/O) characteristics of the computer in detail. In addition, hardware features are included such as size, power, and cooling requirements, as well as compatibility between peripheral equipment and other computers.

Section II contains functional information concerning peripheral equipments commonly used in a 1218 System.

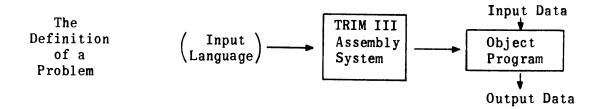

Section III describes the family of TRIM assemblers available with the computer. Since computer memory size and peripheral equipment differ from site to site, three assemblers have been written and are available to satisfy the user's needs.

Section IV describes operator service routines. Operator routines are those routines used by a computer operator, under manual control, to perform computing-center operations. Typical routines of this category are paper tape load, magnetic tape handler, program trace, memory dump, and so forth. Such routines perform a service to the user, but they do not become integrated into his programs. Most of these routines may also be operated under program control.

Section V describes programmer service subroutines. The standard package of programmer service subroutines saves the user time since it contains general subroutines that are used often. These subroutines are supplied in assembler source language for easy integration into the user's program. Subroutines in this category include mathematical, conversion, and assembler support subroutines.

The information contained in this manual is generally written from the stand-point of a UNIVAC 1218 Computer operating in the 1218 mode with exceptions for other modes specifically noted. Therefore, this manual also serves as the programming manual for the UNIVAC 1218 Computer.

The following page is a pre-addressed application for future revisions to this manual. To receive future revisions to the manual, the end user need only fill in the necessary data and return the application by mail.

#### TABLE OF CONTENTS

| Section | <u>Title</u>                            | Page             |

|---------|-----------------------------------------|------------------|

| I       | UNIVAC 1218 Military Computer           | I-1              |

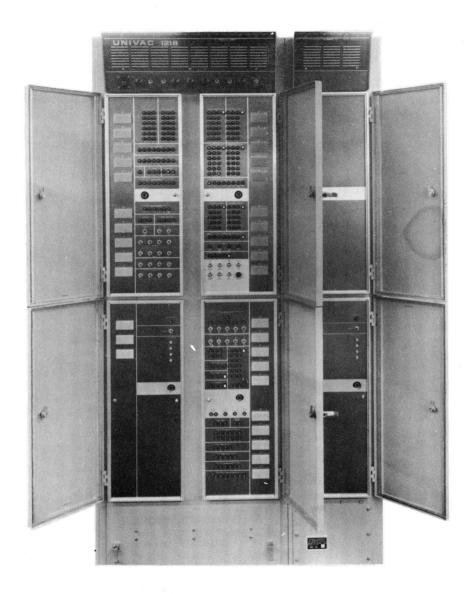

| I – A   | Description of Computer                 | I-A-1            |

|         | 1. General Characteristics              | I-A-1            |

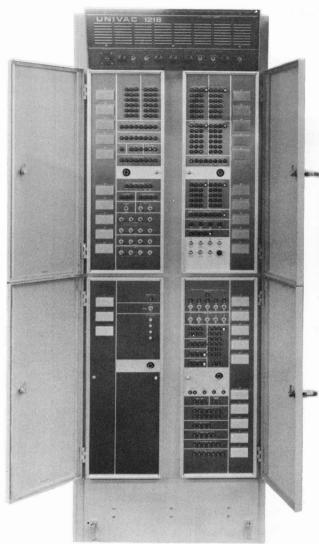

|         | 2. Physical Description                 | I-A-1            |

|         | 2.1 Approximate Size and Weight         | I-A-2            |

|         | 2.2 Environment                         | I-A-2            |

|         | 2.3 Cooling                             | I-A-2            |

|         | 2.4 Power Requirements                  | I-A-2            |

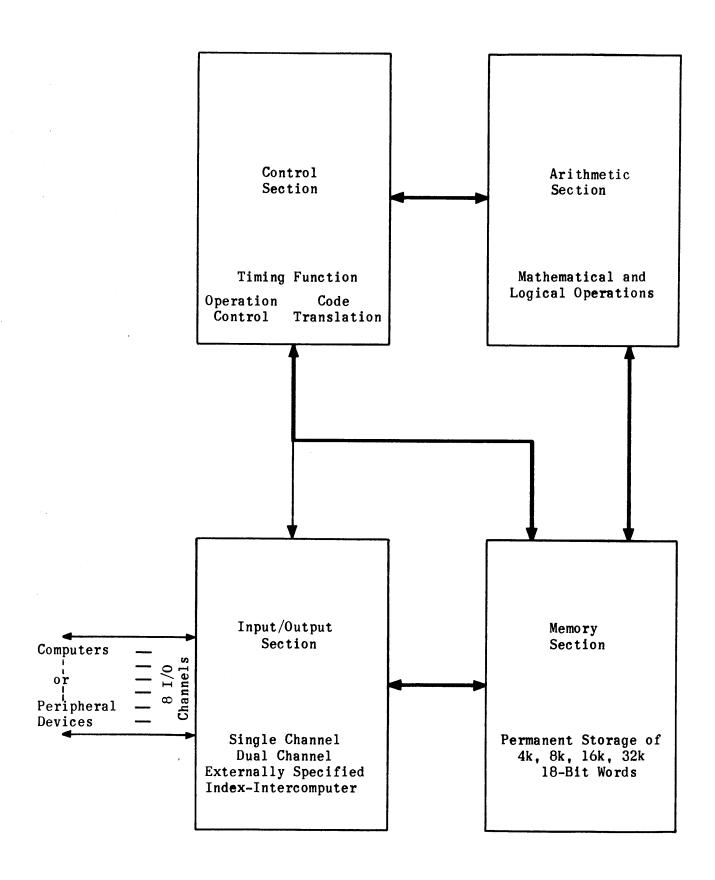

|         | 3. Functional Description               | I-A-2            |

|         | 3.1 Control                             | I-A-2            |

|         | 3.2 Memory                              | I-A-6            |

|         | 3.2.1 Bootstrap Memory                  | I-A-6            |

|         | 3.2.2 Main Memory                       | I-A-6            |

|         | 3.3 Arithmetic                          | I-A-6            |

|         | 3.4 Input/Output (I/O)                  | I-A-6            |

|         | 3.5 Registers and Their Contents        | I-A-7            |

|         | 3.5.1 Addressable Registers             | I-A-7            |

|         | 3.5.2 Non-addressable Registers         | I-A-8            |

|         | 4. Summary of Technical Characteristics | I-A-9            |

|         | 4.1 Memory                              | I-A-9            |

|         | 4.2 Input/Output (I/O)                  | I-A-9            |

|         | 4.2.1 Channels                          | I-A-9            |

|         | 4.2.2 Buffered Transfers                | I-A-9            |

|         | 4.2.3 Operating Modes                   | I-A-9            |

|         | 4.2.4 Transfer Times                    | I-A-10           |

|         | 4.2.5 Interrupts                        | I-A-10           |

|         | 4.2.6 Priority                          | I-A-10           |

|         | 4.2.7 Program Control 4.3 Arithmetic    | I-A-10<br>I-A-10 |

|         |                                         |                  |

|         | 4.4 Control                             | I-A-11           |

| I-B     | Computer Instructions                   | I-B-1            |

|         | 1. General                              | I-B-1            |

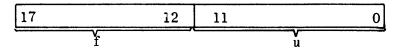

|         | 2. Word Formats                         | I-B-1            |

|         | 2.1 Format I                            | I-B-1            |

|         | 2.2 Format II                           | I-B-2            |

|         | 3. Symbol Conventions                   | I-B-2            |

|         | 4. Instructions                         | I-B-4            |

#### CHANGE 1

| <u>Section</u> | <u>Title</u>                                                                                                                                                                                                                                    | <u>Page</u>                                                    |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| I-B-1          | Transfer Instructions                                                                                                                                                                                                                           | I-B-8                                                          |

|                | <ol> <li>General</li> <li>Instructions</li> </ol>                                                                                                                                                                                               | I-B-8<br>I-B-8                                                 |

| I-B-2          | Arithmetic Instructions                                                                                                                                                                                                                         | I-B-12                                                         |

|                | <ol> <li>General</li> <li>Instructions</li> </ol>                                                                                                                                                                                               | I -B-12<br>I -B-12                                             |

| I-B-3          | Shift Instructions                                                                                                                                                                                                                              | I-B-18                                                         |

|                | <ol> <li>General</li> <li>Instructions</li> </ol>                                                                                                                                                                                               | I -B-18<br>I -B-18                                             |

| I-B-4          | Logical Instructions                                                                                                                                                                                                                            | I-B-21                                                         |

|                | <ol> <li>General</li> <li>Compare Instructions</li> <li>Complement Instructions</li> <li>Selective Set Instruction</li> <li>Selective Clear Instruction</li> <li>Selective Substitute Instructions</li> <li>Parity Skip Instructions</li> </ol> | I -B-21<br>I -B-21<br>I -B-23<br>I -B-24<br>I -B-25<br>I -B-26 |

| I-B-5          | Modifying Instructions                                                                                                                                                                                                                          | I-B-27                                                         |

|                | <ol> <li>General</li> <li>Instructions</li> </ol>                                                                                                                                                                                               | I -B-27<br>I -B-27                                             |

| I-B-6          | Jump Instructions                                                                                                                                                                                                                               | I-B-29                                                         |

|                | <ol> <li>Introduction</li> <li>Unconditional Jump Instructions</li> <li>Conditional Jump Instructions</li> </ol>                                                                                                                                | I -B-29<br>I -B-29<br>I -B-32                                  |

| I-B-7          | Skip and Stop Instructions                                                                                                                                                                                                                      | I-B-37                                                         |

|                | <ol> <li>General</li> <li>Instructions</li> </ol>                                                                                                                                                                                               | I -B-37<br>I -B-37                                             |

| I-B-8          | Input/Output Instructions                                                                                                                                                                                                                       | I-B-40                                                         |

|                | <ol> <li>General</li> <li>Buffer Transfer Instructions</li> <li>Buffer Termination Instructions</li> </ol>                                                                                                                                      | I <b>-</b> B-40<br>I <b>-</b> B-40<br>I <b>-</b> B-42          |

| Section | <u>Title</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|         | 4. Override Instructions 5. Miscellaneous $I/O$ Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I -B-43<br>I -B-44                                                                                           |

| I -C    | Input/Output (I/O) Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I -C -1                                                                                                      |

|         | <ol> <li>General</li> <li>Input/Output Interface</li> <li>2.1 Data Transfers         <ul> <li>2.1.1 Peripheral Operation</li> <li>2.1.2 Intercomputer Operation</li> <li>2.1.3 Forced Transfers (Override)</li> </ul> </li> <li>Interrupts         <ul> <li>2.2.1 Channel Interrupts</li> <li>2.2.2 Special Interrupts</li> </ul> </li> <li>Input/Output Priority</li> <li>Operating Modes         <ul> <li>4.1 Single Channel Mode</li> <li>4.2 Dual Channel Mode</li> <li>4.3 Externally Specified Indexing (ESI) Mode</li> </ul> </li> </ol> | I-C-1 I-C-3 I-C-3 I-C-7 I-C-7 I-C-7 I-C-8 I-C-9 I-C-9 I-C-10 I-C-11 I-C-11 I-C-14                            |

| II      | Peripheral Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | II-1                                                                                                         |

| II-A    | UNIVAC 1232 Input/Output Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | II-A-1                                                                                                       |

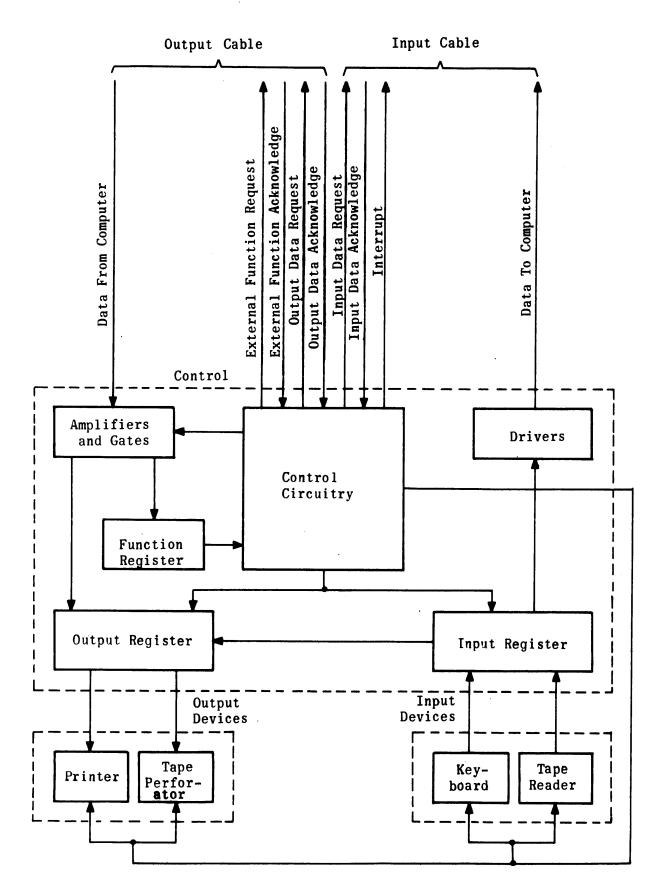

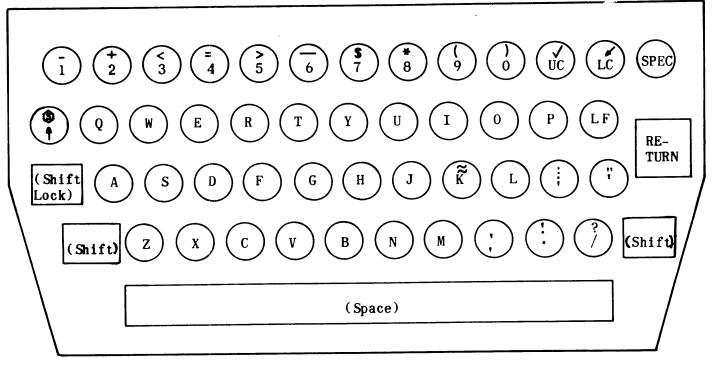

|         | <ol> <li>Basic Information         1.1 On-Line Operation         1.2 Off-Line Operation         2. Input/Output Control         2.1 Computer Control         2.2 Panel Control         3. Operation of Units         3.1 Perforated Tape Reader         3.2 Tape Perforator         3.3 Printer         3.4 Keyboard         3.5 Keyboard Interrupt         3.6 Switches and Indicators         3.7 External Function Manual Controls</li> </ol>                                                                                                | II-A-1<br>II-A-1<br>II-A-1<br>II-A-1<br>II-A-5<br>II-A-5<br>II-A-7<br>II-A-7<br>II-A-7<br>II-A-11<br>II-A-11 |

| Section | <u>Title</u>                                                                                                                                                                                                                                                                                                        | <u>Page</u>                                                                   |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

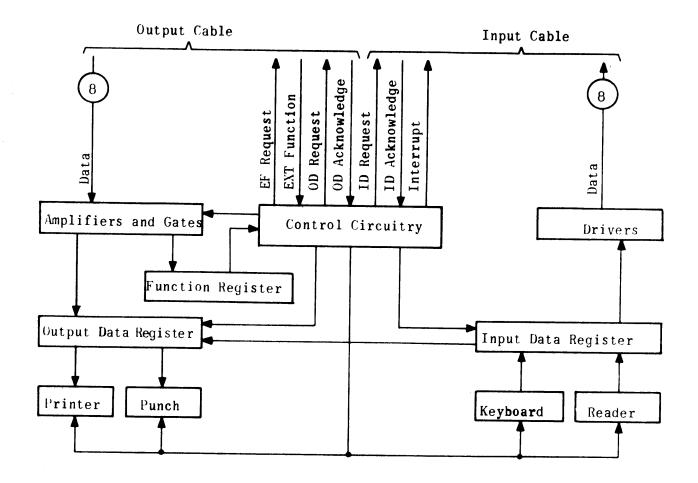

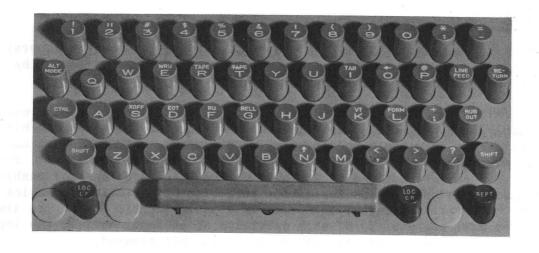

| II-B    | UNIVAC 1532 Input/Output Console                                                                                                                                                                                                                                                                                    | II-B-1                                                                        |

|         | <ol> <li>General Description</li> <li>1.1 Operational Characteristics</li> <li>1.1.1 On-line Mode</li> <li>1.1.2 Off-line Mode</li> </ol>                                                                                                                                                                           | II-B-1<br>II-B-1<br>II-B-1<br>II-B-2                                          |

|         | 2. Functional Description 2.1 General 2.2 Punching Output Data 2.3 Printing Output Data 2.4 Reading Input Data 2.5 Keyboard Input 2.6 Function Instructions                                                                                                                                                         | II-B-2<br>II-B-2<br>II-B-2<br>II-B-3<br>II-B-3<br>II-B-5<br>II-B-6            |

|         | 3. Programming Considerations 3.1 General 3.2 Tape Reading Procedures 3.3 Keyboard Input Procedures 3.3.1 Keyboard-Printer Entry Via Interrupt 3.3.2 Keyboard-Printer Entry Via Computer                                                                                                                            | II-B-6<br>II-B-6<br>II-B-7<br>II-B-7<br>II-B-7                                |

|         | Commands 3.4 Tape Punching Procedures 3.5 Printer Procedures 3.6 Off-line Operations                                                                                                                                                                                                                                | II-B-8<br>II-B-8<br>II-B-8<br>II-B-8                                          |

| II-c    | Magnetic Tape System (Type 1240A)                                                                                                                                                                                                                                                                                   | II-C-1                                                                        |

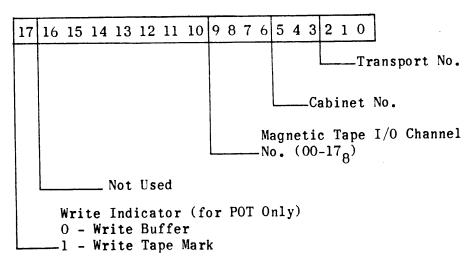

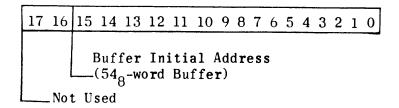

|         | <ol> <li>Basic Information</li> <li>Input/Output Sequence for 1240A Magnetic Tape<br/>System</li> <li>Address Word</li> </ol>                                                                                                                                                                                       | II-C-1<br>II-C-1<br>II-C-4                                                    |

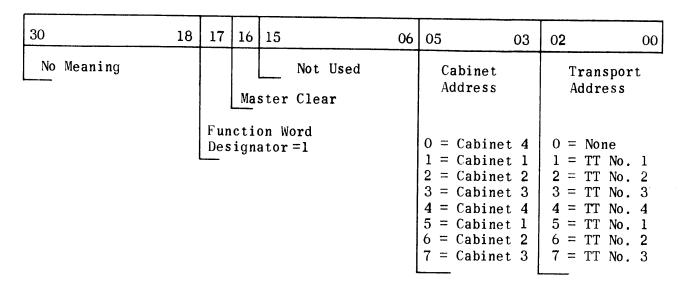

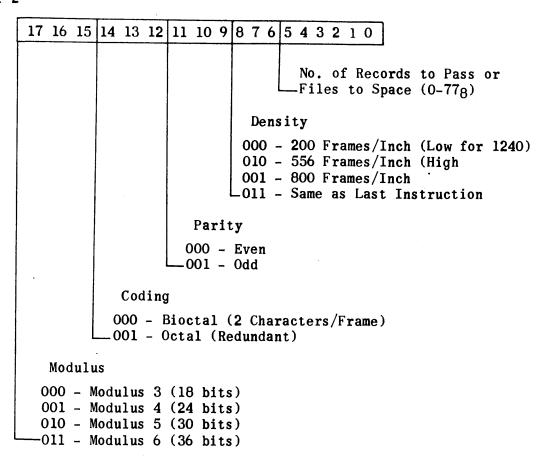

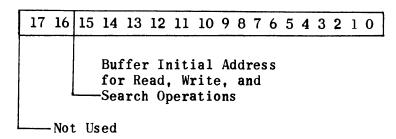

|         | 2.2 Instruction Word  3. Interrupt and Status Word  4. Magnetic Tape Operations 4.1 Master Clear (Bit 16) 4.2 Read (Bit 11-15) 4.3 Write (Bit 11-15) 4.4 Rewind (Bits 11-15) 4.5 Rewind-Read (Bits 11-15) 4.6 Space File Forward/Backward (Bits 11-15) 4.7 Write Tape Mark (Bits 11-15) 4.8 Back Space (Bits 11-15) | II-C-4 II-C-4 II-C-7 II-C-7 II-C-7 II-C-9 II-C-9 II-C-9 II-C-9 II-C-9 II-C-10 |

|         | 4.9 Search (Bits 11-15) 5. Format Portion of Instruction Word 5.1 Modulus 5.2 Character 5.3 Parity 5.4 Density                                                                                                                                                                                                      | II-C-10<br>II-C-10<br>II-C-11<br>II-C-11<br>II-C-11                           |

| Section | <u>Title</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                                                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

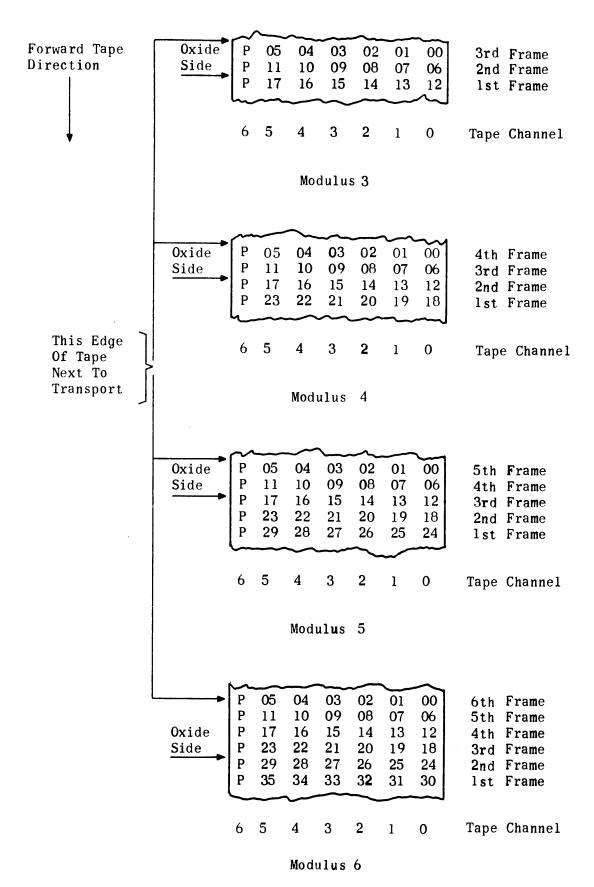

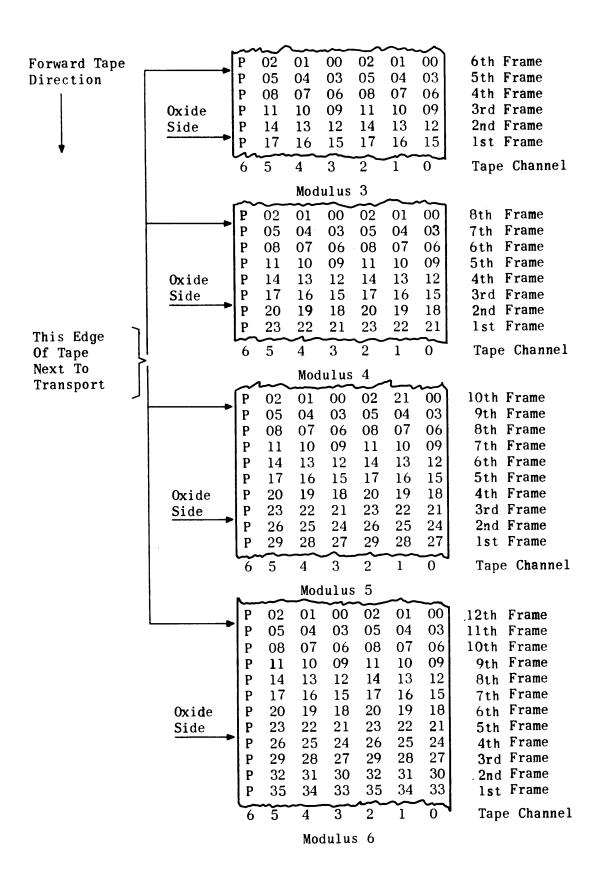

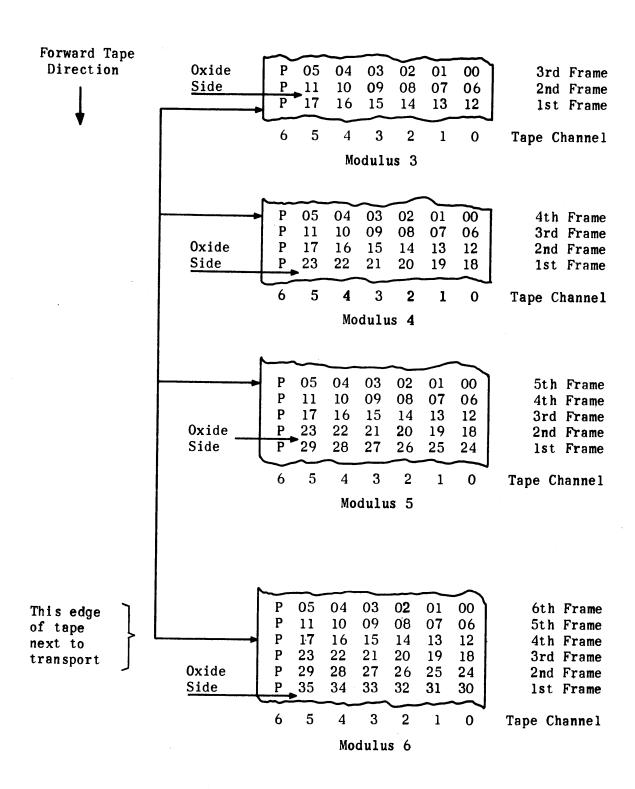

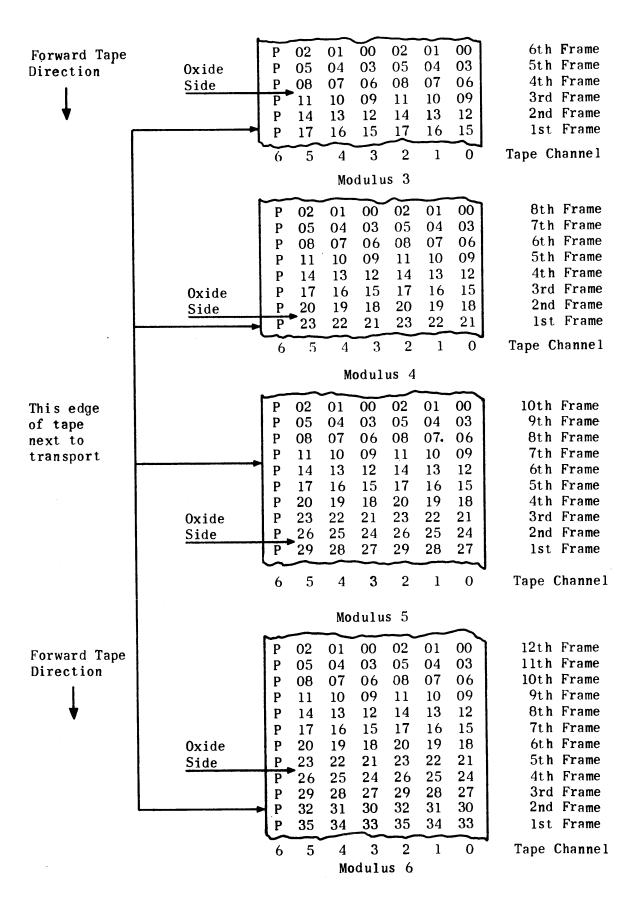

|         | 6. Tape System Moduli 6.1 Modulus 3: (Bits 10 and 09 = 00) 6.2 Modulus 4: (Bits 10 and 09 = 01) 6.3 Modulus 5: (Bits 10 and 09 = 10) 6.4 Modulus 6: (Bits 10 and 09 = 11)                                                                                                                                                                                                                                                                                              | II -C -12<br>II -C -12<br>II -C -12<br>II -C -12                                                                                            |

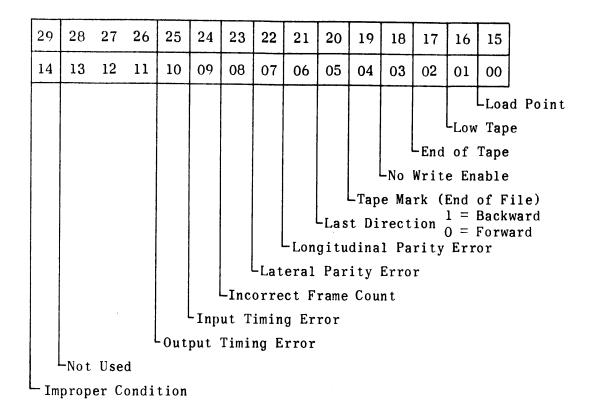

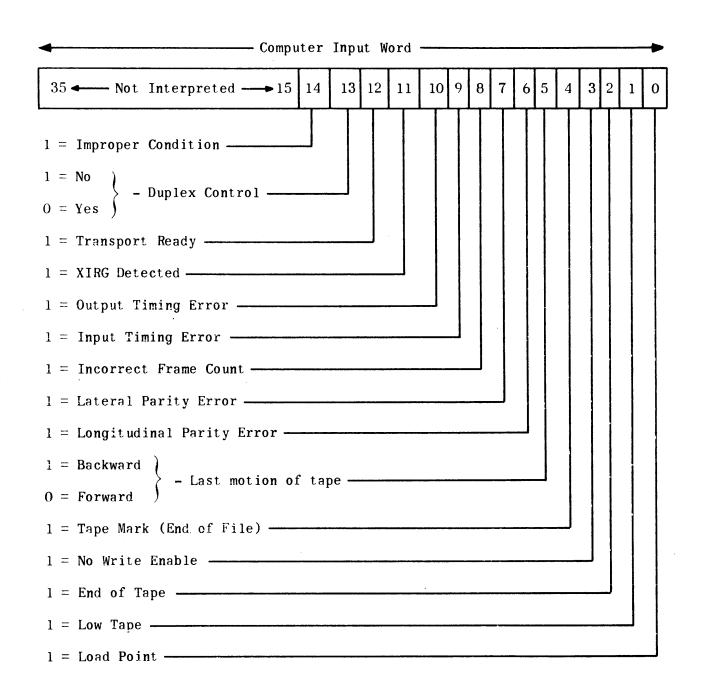

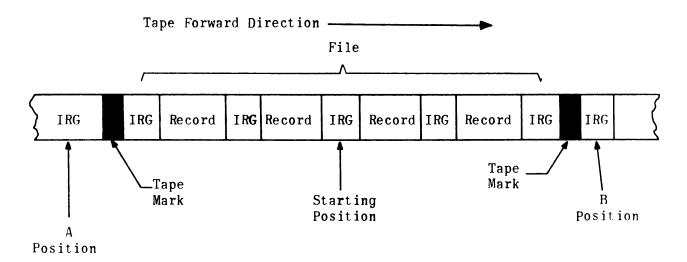

|         | 6.4 Modulus 6: (Bits 10 and 09 = 11)  7. Status Word  7.1 Improper Condition (Bits 29 and 14)  7.2 Output Timing Error (Bits 25 and 10)  7.3 Input Timing Error (Bits 24 and 09)  7.4 Incorrect Frame Count (Bits 23 and 09)  7.5 Lateral Parity Error (Bits 22 and 07)  7.6 Last Tape Motion (Bits 20 and 05)  7.7 Longitudinal Parity Error (Bits 21 and 06)  7.8 Tape Mark (Bits 19 and 04)  7.9 No Write Enable (Bits 18 and 03)                                   | II-C-12<br>II-C-15<br>II-C-16<br>II-C-16<br>II-C-16<br>II-C-16<br>II-C-17<br>II-C-17                                                        |

|         | 7.10 End of Tape (Bits 17 and 02) 7.11 Low Tape (Bits 16 and 01) 7.12 Load Point (Bits 15 and 00) 8. Tape Markers 9. Logical Selection of Tape Transports 10. 1240A High Speed Printer Off-line Compatibility 11. Programming Considerations 11.1 General 11.2 Write Procedures 11.3 Read Procedures 11.4 Search Procedures 11.5 Record Length 11.6 End of File 11.7 Editing of Tape 11.8 Bad Tape                                                                     | II-C-17<br>II-C-17<br>II-C-18<br>II-C-18<br>II-C-19<br>II-C-19<br>II-C-20<br>II-C-21<br>II-C-21<br>II-C-23<br>II-C-23<br>II-C-23<br>II-C-23 |

| II-D    | Magnetic Tape System (Type 1540/1541)                                                                                                                                                                                                                                                                                                                                                                                                                                  | II-D-1                                                                                                                                      |

|         | <ol> <li>General Information</li> <li>Performance of Function</li> <li>Duplexing</li> <li>Tape Markers</li> <li>Status Word and Interrupt (Status Interrupt)         <ul> <li>Improper Condition (Bit 14 = 1)</li> <li>Duplex Control (Bit 13; 0 = In Control; 1 = Not In Control)</li> <li>Transport Ready (Bit 12 = 1)</li> <li>XIRG Detected (Bit 11 = 1)</li> <li>Output Timing Error (Bit 10 = 1)</li> <li>Input Timing Error (Bit 09 = 1)</li> </ul> </li> </ol> | II-D-1<br>II-D-3<br>II-D-3<br>II-D-5<br>II-D-7<br>II-D-7<br>II-D-8<br>II-D-8<br>II-D-8<br>II-D-8<br>II-D-9                                  |

#### CHANGE 1

| Section |    |                  | · ·      | <u> Title</u>                                         | <u>Page</u> |

|---------|----|------------------|----------|-------------------------------------------------------|-------------|

|         |    |                  |          | Error (Bit 07 = 1)                                    | II-D-9      |

|         |    |                  |          | rity Error (Bit $06 = 1$ )                            | II-D-9      |

|         |    |                  |          | n (Bit 05; 1 = Backward                               |             |

|         |    | 0 = Fo           |          | - 4                                                   | II-D-10     |

|         |    | 5.11 Tape M      |          |                                                       | II-D-10     |

|         |    |                  |          | (Bit 03 = 1)                                          | II-D-10     |

|         |    | 5.13 End of      |          |                                                       | II-D-10     |

|         |    | 5.14 Low Ta      |          |                                                       | II-D-10     |

|         | ,  | 5.15 Load P      |          |                                                       | II-D-10     |

|         | 6. |                  |          | mmands - Function Words                               | II-D-10     |

|         |    |                  | (Bits 10 |                                                       | II-D-11     |

|         |    |                  |          | nator (Bit 8); 1 Selects                              | TT 5        |

|         |    |                  | 0 Select | s Bioctal                                             | II-D-11     |

|         |    | 6.3 Modulu       |          | 0 (D 1 . D1. 10 .                                     | II-D-15     |

|         |    | 6.3.1            |          | 3 (Designator Bits 10 and                             | TT D 15     |

|         |    | / 0.0            | 09 = 00  | 4 /D                                                  | II-D-15     |

|         |    | 6.3.2            |          | 4 (Designator Bits 10 and                             | TT D 15     |

|         |    | / n n            | 09 = 01  |                                                       | II-D-15     |

|         |    | 6.3.3            |          | 5 (Designator Bits 10 and                             | TT D 15     |

|         |    |                  | 09 = 10  |                                                       | II-D-15     |

|         |    | 6.3.4            |          | 6 (Designator Bits 10 and                             | II-D-15     |

|         |    | 4 A Danisa       | 09 = 11  |                                                       | 11-0-13     |

|         |    |                  |          | or (Bit 7), 1 Selects Odd,                            | II-D-17     |

|         |    |                  | cts Even | ton (Dita 4 and 5)                                    | II-D-17     |

|         |    |                  |          | tor (Bits 6 and 5)                                    | II-D-17     |

|         |    | 6.6 Operat 6.6.1 | ion Code | wations                                               | II-D-17     |

|         |    | 0.0.1            |          | Read-Forward                                          | II-D-17     |

|         |    |                  |          | Read-Backward                                         | II-D-19     |

|         |    |                  |          |                                                       | II-D-19     |

|         |    |                  |          | Read-Modified Stop<br>Selective Read-Forward/Backward | II-D-19     |

|         |    | 6.6.2            |          | eration - General Information                         | II-D-19     |

|         |    | 0.0.2            | 6.6.2.1  |                                                       | II-D-20     |

|         |    |                  |          | Write - Ignore Error Halt                             | II-D-20     |

|         |    |                  | 6.6.2.3  |                                                       | 11-0-20     |

|         |    |                  |          | Gap (XIRG)                                            | II-D-21     |

|         |    |                  |          | Write Tape Mark                                       | II-D-21     |

|         |    | 6.6.3            |          | le - Forward/Backward                                 | II-D-21     |

|         |    | 6.6.4            | •        | 1e - Folward/Dackward                                 | II-D-21     |

|         |    | 6.6.5            |          | ction Operations (General                             | 11 5 21     |

|         |    | 0.0.3            | Informat |                                                       | II-D-22     |

|         |    |                  | 6.6.5.1  | Search (Type I and Type II -                          | 11 0-42     |

|         |    |                  | 0.0.5.1  | Forward/Backward)                                     | II-D-22     |

|         |    |                  | 6.6.5.2  | Search File Forward/Backward                          | II-D-23     |

|         |    |                  |          | Rewind-Read                                           | II-D-23     |

|         |    |                  | 0.0.0.0  | n cmilia_n caa                                        | エエーレーとり     |

| Section | <u>Title</u>                                                                                                  | Page                          |

|---------|---------------------------------------------------------------------------------------------------------------|-------------------------------|

|         | 6.6.5.4 Rewind-Clear Write Enable<br>6.6.5.5 Rewind-Read-Clear Write Enable<br>6.6.6 Request Transport Status | II-D-23<br>II-D-23<br>II-D-23 |

|         | 6.6.7 Transmit Extra (Bits 17, 16 and 6 = 1, 0 and 1, Respectively)                                           | II-D-24                       |

|         | <ol> <li>Magnetic Tape Unit - High-Speed Printer Off-line<br/>Capability</li> </ol>                           | II-D-24                       |

|         | 8. Operating Instructions                                                                                     | II-D-27                       |

|         | 9. Sequence of Events                                                                                         | II-D-27                       |

| II-E    | UNIVAC High-Speed Printer (Model 1469)                                                                        | II-E-1                        |

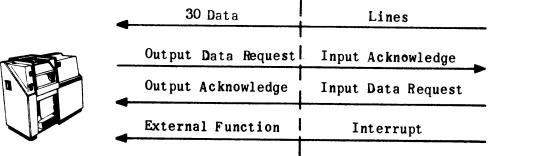

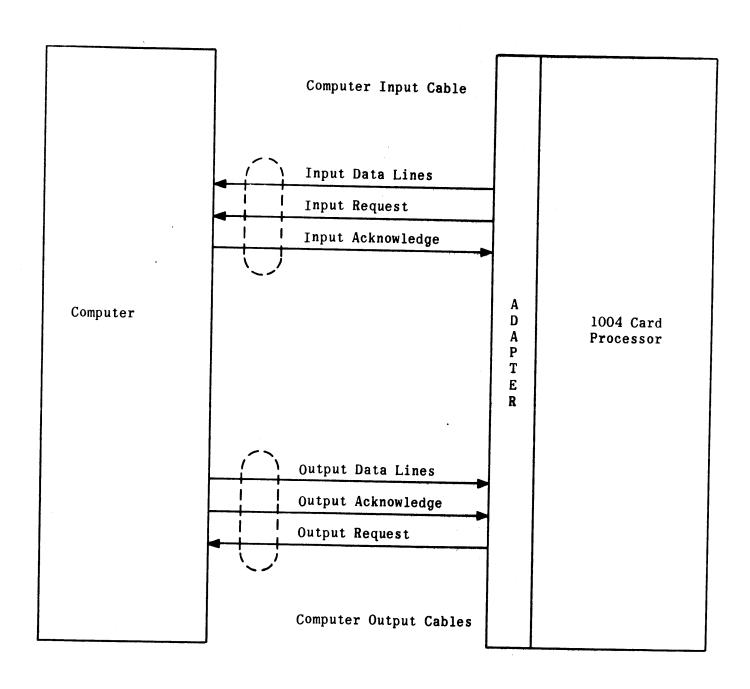

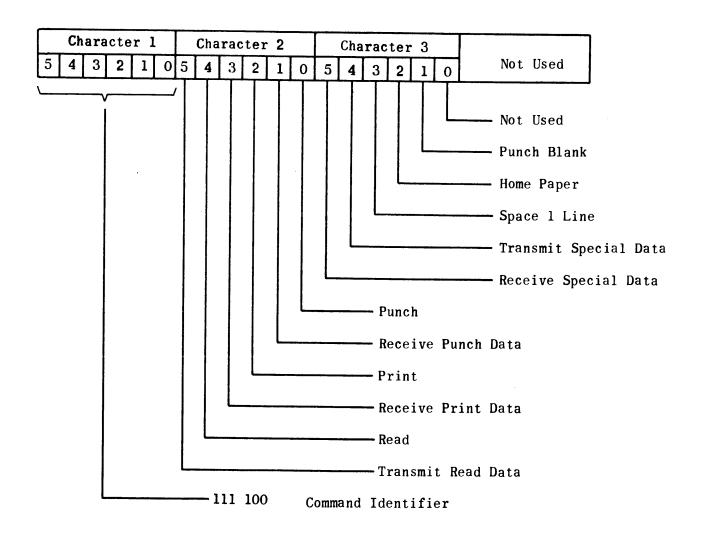

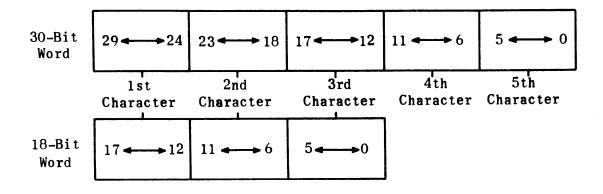

| II-F    | (This section has been intentionally omitted.)  UNIVAC 1004 Card Processor                                    | II-F-1                        |

| 11 1    |                                                                                                               |                               |

|         | 1. Basic Information                                                                                          | II-F-1                        |

|         | <ol> <li>Message and Word Formats</li> <li>Manual Operating Procedures</li> </ol>                             | II-F-6                        |

|         | 3.1 Card Reader                                                                                               | II-F-10<br>II-F-11            |

|         | 3.2 Card Punch                                                                                                | II-F-11                       |

|         | 3.3 High-Speed Printer                                                                                        | II-F-11                       |

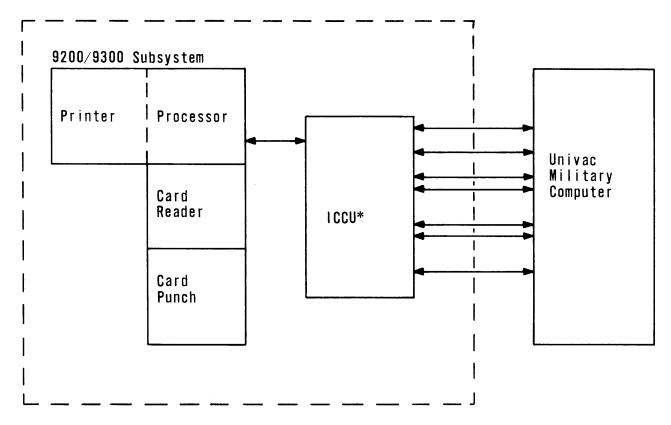

| II-G    | UNIVAC 9200/9300 Subsystem                                                                                    | II-G-1                        |

|         | 1. General Information                                                                                        | II-G-1                        |

|         | 2. Military Computer/ICCU Interface                                                                           | II-G-1                        |

|         | 2.1 Introduction                                                                                              | II-G-1                        |

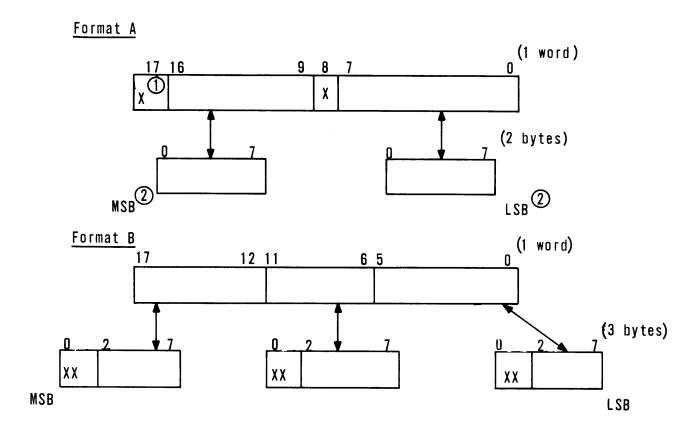

|         | 2.2 Data Formats                                                                                              | II-G-1                        |

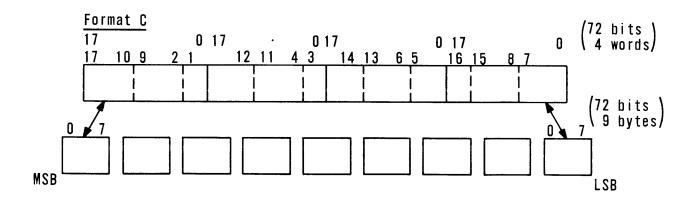

|         | 2.2.1 ICCU Data Transfer Formats                                                                              | II-G-3                        |

|         | 2.2.2 Header Formats                                                                                          | II-G-3                        |

|         | 2.3 Header Information                                                                                        | II-G-3                        |

|         | 2.3.1 Message Header Format                                                                                   | II-G-3                        |

|         | 2.3.1 Message neader rollman                                                                                  | II-G-13                       |

| Section |    |      | <u>Title</u>                          | <u>Page</u> |

|---------|----|------|---------------------------------------|-------------|

|         |    | 2.4  | Control Word Formats                  | II-G-12     |

|         |    |      | 2.4.1 Master External Function Word   | II-G-12     |

|         |    |      | 2.4.2 External Interrupt Status Word  | II-G-12     |

|         |    |      | 2.4.2.1 Error Status                  | II-G-13     |

|         |    |      | 2.4.2.2 Command Byte                  | II-G-13     |

|         |    | 2.5  | Initiation Sequnce                    | II-G-14     |

|         |    | 2.6  | Data Transfer Sequences               | II-G-14     |

|         |    |      | 2.6.1 Output Data Transfer            | II-G-14     |

|         |    |      | 2.6.2 Input Data Transfer             | II-G-15     |

|         |    |      | 2.6.3 Special Functions               | II-G-15     |

|         |    |      | 2.6.3.1 Output Data Transfer          | II-G-16     |

|         |    |      | 2.6.3.2 Input Data Transfer           | II-G-16     |

|         |    |      | 2.6.4 Maintenance Data Turnaround     | II-G-17     |

|         |    |      | Error Notification                    | II-G-17     |

|         | 3. | 9200 | 0/9300/ICCU Interface                 | II-G-17     |

|         |    |      | Introduction                          | II-G-17     |

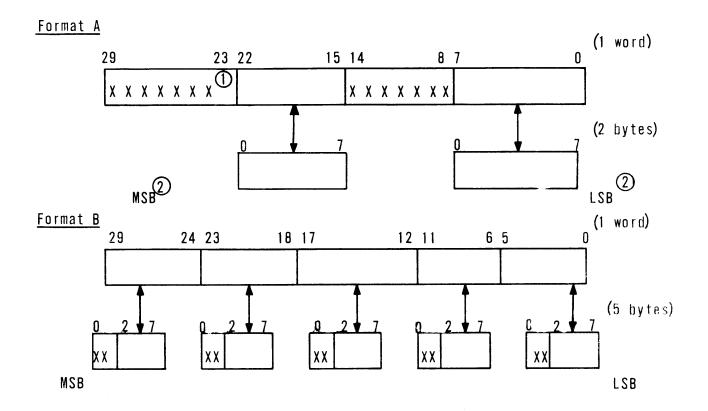

|         |    | 3.2  | Data Formats                          | II-G-18     |

|         |    |      | 3.2.1 ICCU Data Transfer Formats      | II-G-18     |

|         |    |      | 3.2.2 Header Formats                  | II-G-18     |

|         |    |      | Header Information                    | II-G-18     |

|         |    | 3.4  | · · · · · · · · · · · · · · · · · · · | II-G-18     |

|         |    |      | 3.4.1 Slave Command Byte              | II-G-18     |

|         |    |      | 3.4.2 Slave Status Byte               | II-G-19     |

|         |    |      | 3.4.3 Sense Byte Formats              | II-G-20     |

|         |    |      | 3.4.3.1 Sense Byte 1                  | II-G-20     |

|         |    |      | <b>3.4.3.2</b> Sense Byte 4           | II-G-21     |

|         |    | 3.5  | Initiation Sequence                   | II-G-22     |

|         |    | 3.6  | Data Transfer Sequences               | II-G-22     |

|         |    |      | 3.6.1 Input Data Transfer             | II-G-22     |

|         |    |      | 3.6.2 Output Data Transfer            | II-G-23     |

|         |    |      | 3.6.3 Special Functions               | II-G-23     |

|         |    |      | 3.6.3.1 Input Data Transfer           | II-G-24     |

|         |    |      | 3.6.3.2 Output Data Transfer          | II-G-24     |

|         |    |      | 3.6.4 Maintenance Data Turnaround     | II-G-24     |

|         |    | 3.7  | Error Notification                    | II-G-25     |

|         | 4. |      | /9300 Operating Procedures            | II-G-25     |

|         |    | 4.1  | , F J                                 | II-G-25     |

|         |    | 4.2  | Initializing Procedures               | II-G-25     |

|         |    |      | 4.2.1 Power                           | II-G-27     |

|         |    |      | 4.2.2 Printer                         | II-G-27     |

|         |    |      | 4.2.3 Card Reader                     | II-G-27     |

|         |    |      | 4.2.4 Card Punch                      | II-G-27     |

|         |    | 4.3  | o o                                   | II-G-28     |

|         |    | 4.4  | Running and Stopping                  | II-G-29     |

|         |    |      | 4.4.1 Manual Stopping                 | II-G-29     |

|         |    |      | 4.4.2 Automatic Stopping              | II-G-29     |

|         |    |      | 4.4.3 Power                           | 11_6_29     |

| Section | <u>Title</u>                                                                                                                                                                                      | <u>Page</u>                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| III     | 4.5 Programmed Halting 4.6 Abnormal Stopping 4.6.1 Abnormal Stop Indications 4.6.2 Abnormal Conditions 4.6.2.1 Printer 4.6.2.2 Card Reader 4.6.2.3 Card Punch 4.6.2.4 Processor  Assembly Systems | II-G-29<br>II-G-30<br>II-G-30<br>II-G-31<br>II-G-34<br>II-G-36<br>II-G-39<br>III-1 |

|         | - ·                                                                                                                                                                                               | III-1                                                                              |

|         | 1. TRIM I<br>2. TRIM II                                                                                                                                                                           | III-1                                                                              |

|         |                                                                                                                                                                                                   | III-1                                                                              |

|         | 3. TRIM III                                                                                                                                                                                       | 111-1                                                                              |

| III-A   | TRIM I Assembly System                                                                                                                                                                            | III-A-1                                                                            |

|         | 1. Basic Information                                                                                                                                                                              | III-A-1                                                                            |

|         | 2. Symbolic Addressing                                                                                                                                                                            | III-A-1                                                                            |

|         | 2.1 Labels                                                                                                                                                                                        | III-A-1                                                                            |

|         | 2.2 Tags                                                                                                                                                                                          | III-A-1                                                                            |

|         | 3. Input Language Format                                                                                                                                                                          | III-A-2                                                                            |

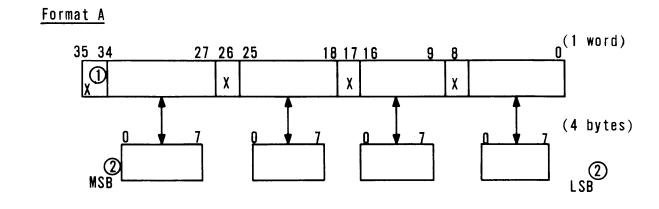

|         | 3.1 Format A                                                                                                                                                                                      | III-A-3                                                                            |

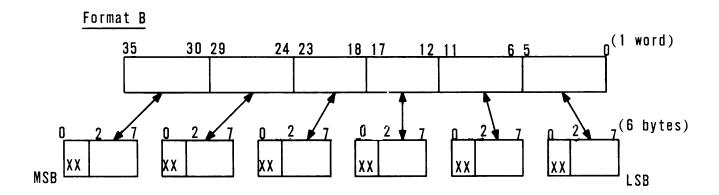

|         | 3.2 Format B                                                                                                                                                                                      | III-A-4                                                                            |

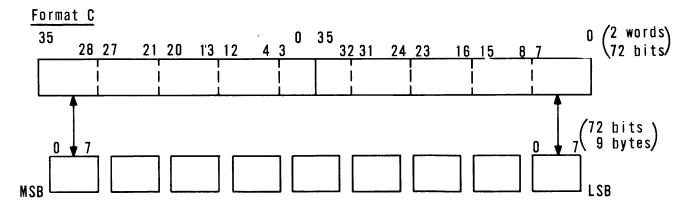

|         | 3.3 Format C                                                                                                                                                                                      | III-A-4                                                                            |

|         | 4. Special Operators                                                                                                                                                                              | III-A-5                                                                            |

|         | 5. The LOK Tag                                                                                                                                                                                    | III-A-7                                                                            |

|         | 6. Input Tape Format                                                                                                                                                                              | III-A-7                                                                            |

|         | 7. TRIM I Outputs                                                                                                                                                                                 | III-A-7                                                                            |

|         | 8. Ground Rules                                                                                                                                                                                   | III-A8                                                                             |

|         | 9. Loading and Operating Procedures                                                                                                                                                               | III-A-10                                                                           |

|         | 9.1 Loading the Assembler                                                                                                                                                                         | III-A-10                                                                           |

|         | 9.2 Using the Assembler                                                                                                                                                                           | III-A-10                                                                           |

|         | 9.3 Error Detection and Display                                                                                                                                                                   | III-A-11                                                                           |

| III-B   | TRIM II Assembly System                                                                                                                                                                           | III-B-1                                                                            |

|         | 1. Introduction                                                                                                                                                                                   | III-B-1                                                                            |

|         | 2. Description                                                                                                                                                                                    | III-B-1                                                                            |

|         | 2.1 Source Language                                                                                                                                                                               | III-B-1                                                                            |

|         | 2.1.1 Label                                                                                                                                                                                       | III-B-4                                                                            |

|         | 2.1.2 Statement                                                                                                                                                                                   | III-B-4                                                                            |

|         | 2.1.2.1 Operator                                                                                                                                                                                  | III-B-4                                                                            |

|         | 2.1.2.2 Operand(s)                                                                                                                                                                                | III-B-5                                                                            |

|         | 2.1.3 Notes                                                                                                                                                                                       | III-B-5                                                                            |

|         | 2 1 4 Symbols                                                                                                                                                                                     | III-B-5                                                                            |

| Section |              | <u>Title</u>                                                                          | <u>Page</u>          |

|---------|--------------|---------------------------------------------------------------------------------------|----------------------|

|         | 2.2          |                                                                                       | III-B-0              |

|         |              | 2.2.1 Allocation Header (ALLOC)                                                       | III-B-6              |

|         |              | 2.2.2 Program Header (PROG)                                                           | III-B-7              |

|         |              | 2.2.3 DEBUG Declarative                                                               | III-B-7              |

|         | 2.3          | •                                                                                     | III-B-8              |

|         |              | 2.3.1 Format A                                                                        | III-B-8              |

|         |              | 2.3.2 Format B                                                                        | III-B-9              |

|         | 0. 4         | 2.3.3 Format C                                                                        | III-B-9<br>III-B-10  |

|         | 2.4          | Poly-Operations                                                                       | III-B-10             |

|         |              | 2.4.1 Reserve Operation (RESERV)                                                      | III-B-10<br>III-B-11 |

|         |              | 2.4.2 CLEAR Operation                                                                 | III-B-11<br>III-B-12 |

|         |              | 2.4.3 MOVE Operation                                                                  | III-B-12<br>III-B-14 |

|         |              | 2.4.4 I/O Operations                                                                  | III-B-14             |

|         |              | 2.4.5 REMARK Operation                                                                | III-B-15             |

|         |              | 2.4.6 DATA Operation                                                                  | III-B-16             |

|         |              | 2.4.7 Punch Contents Operation (PCHC)                                                 | III-B-10             |

|         |              | 2.4.8 Punch Text Operation (PCHT)                                                     | III-B-17             |

|         |              | 2.4.9 Type Text Operation (TYPT)                                                      | III-B-18             |

|         |              | <pre>2.4.10 Type Contents Operation (TYPC) 2.4.11 Double Set Operation (DBLSET)</pre> | III-B-19             |

|         |              |                                                                                       | III-B-19             |

|         | 0. 5         | 2.4.12 SETSR Operation                                                                | III-B-20             |

|         | 2.5          |                                                                                       | III-B-20             |

|         | 2.6          | -                                                                                     | III-B-21             |

|         |              | ogramming Procedures                                                                  | III-B-22             |

|         | 3. ]         | •                                                                                     | III-B-22             |

|         | 3.2          |                                                                                       | III-B-24             |

|         |              | ading and Operating Procedures                                                        | III-B-24             |

|         | 4. I<br>4. 2 | <u> </u>                                                                              | III-B-24             |

|         | 4.3          |                                                                                       | III-B-25             |

|         | 4            | 4.3.1 Set Base Address in AL                                                          | III-B-25             |

|         |              | 4.3.2 Illegal Output Reselect in AL                                                   | III-B-26             |

|         |              | 4.3.3 UNALLOC TAGS                                                                    | III-B-26             |

|         |              | 4.3.4 DUP LBL                                                                         | 111-B-26             |

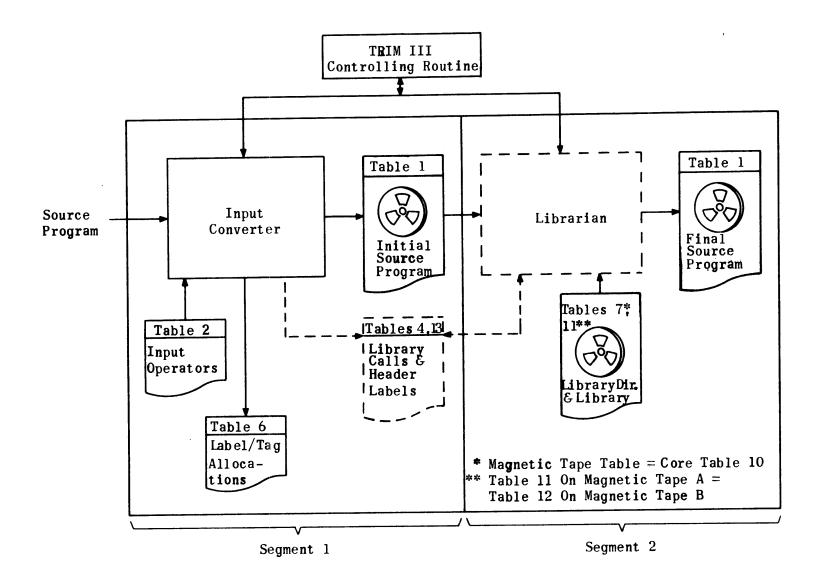

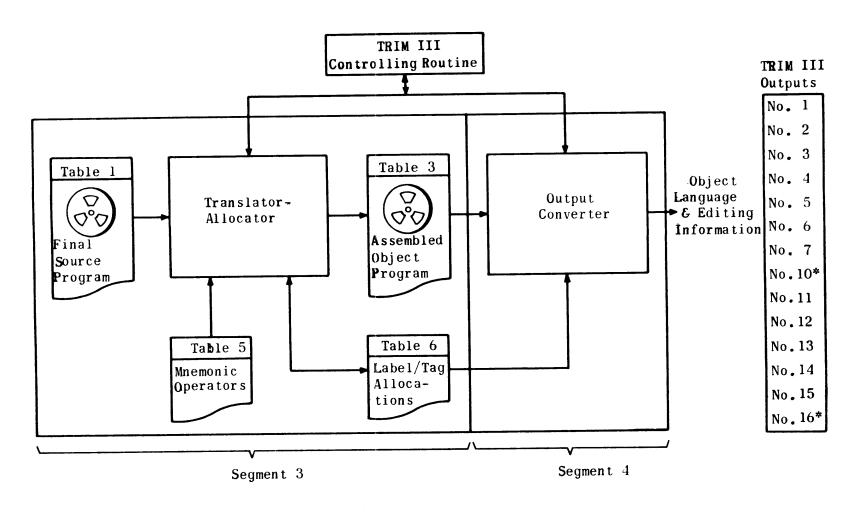

| III-C   | TRIM I       | II Assembly System                                                                    | III-C-1              |

|         | l. Int       | troduction                                                                            | III-C-1              |

|         | 2. De:       | scription                                                                             | II I-C-1             |

|         | 2.           | l Source Language                                                                     | III-C-4              |

|         |              | 2.1.1 Label                                                                           | III-C-4              |

|         |              | 2.1.2 Statement                                                                       | III-C-5              |

|         |              | 2.1.2.1 Operator                                                                      | III-C-5              |

|         |              | 2.1.2.2 Operand(s)                                                                    | III-C-5              |

|         |              | 2.1.3 Notes                                                                           | III-C <b>-</b> 5     |

|         |              | 2.1.4 Symbols                                                                         | III-C-5              |

| Section |   |                  | <u>Title</u>              | <u>Page</u>          |

|---------|---|------------------|---------------------------|----------------------|

|         | 2 | 2 Header and De  | eclarative Operations     | III-C-6              |

|         |   | 2.2.1 Contro     | ol Header (CONTR)         | III-C-6              |

|         |   | 2.2.2 Alloca     | ntion Header (ALLOC)      | III-C-8              |

|         |   | 2.2.3 Progra     | m Header (PROG)           | III-C-8              |

|         |   | 2.2.4 Correc     | tion Header (CORREC)      | III-C-9              |

|         |   | 2.2.5 DEBUG      | Decl <b>arative</b>       | III-C-9              |

|         |   | 2.2.6 OUTPUT     | ' Declarative             | III-C-11             |

|         |   | 2.2.7 DECKI      | ) Declarative             | III-C-11             |

|         |   | 2.2.8 ENDATA     | A Declarative             | III-C-11             |

|         | 2 | 3 Mono-Operation | ns                        | III-C-12             |

|         |   | 2.3.1 Format     | ; <b>A</b>                | III-C-12             |

|         |   | 2.3.2 Format     | , B                       | III-C-13             |

|         |   | 2.3.3 Format     | ; <b>C</b>                | III-C-13             |

|         | 2 | 4 Poly-Operation | ns                        | III-C-13             |

|         |   | 2.4.1 Reserv     | re Operation (RESERV)     | III-C-14             |

|         |   | 2.4.2 CLEAR      | Operation                 | III-C-14             |

|         |   | 2.4.3 MOVE 0     | )peration                 | III-C-16             |

|         |   | 2.4.4 	 I/0 	 Op | perations                 | III-C-17             |

|         |   |                  | ry CALL Operation         | III-C-18             |

|         |   | 2.4.6 REMARI     | <pre>&lt; Operation</pre> | III-C-19             |

|         |   | 2.4.7 DATA (     |                           | III-C-19             |

|         |   |                  | Contents Operation (PCHC) | III-C-19             |

|         |   |                  | Text Operation (PCHT)     | III-C-21             |

|         |   | 2.4.10 Type (    | Contents Operation (TYPC) | III-C-21             |

|         |   | 2.4.11 Type 7    | Text Operation (TYPT)     | III-C-22             |

|         |   |                  | eset Operation            | III-C-23             |

|         |   | 2.4.13 SETSR     | Operation                 | III-C-23             |

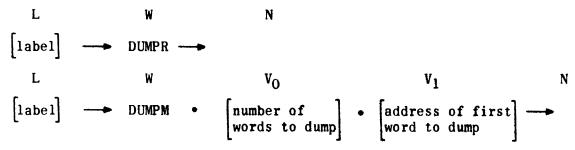

|         |   | 5 Debugging Oper |                           | III-C-24             |

|         |   | 6 TRIM III Outpu |                           | III-C-26             |

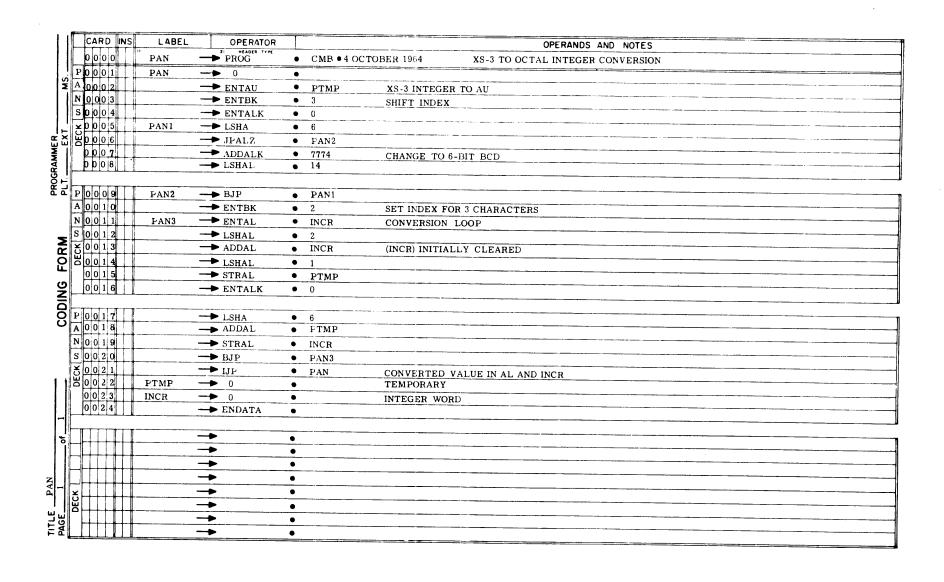

|         |   | ogramming Proced |                           | III-C-27             |

|         | 3 | l Paper Tape In  |                           | III-C-27             |

|         |   |                  | ard Correction Methods    | III-C-27             |

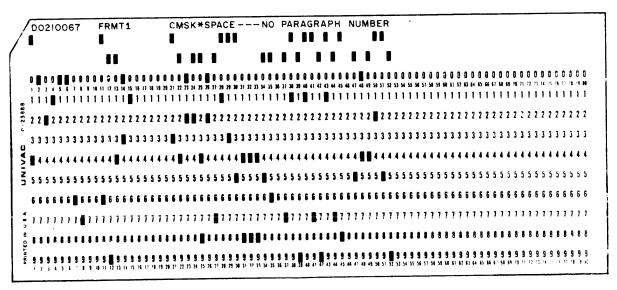

|         |   | 2 80-Column Car  |                           | III-C-28             |

|         |   |                  | e Input Format            | III-C-31             |

|         | 3 | 4 Source Progra  | am Corrections            | III-C-31             |

|         |   |                  | Tape Correction Format    | III-C-32             |

|         |   |                  | Correction Format         | III-C-32             |

|         |   | 5 Ground Rules   |                           | III-C-34             |

|         |   |                  | and Operating Procedures  | III-C-35             |

|         |   | l Basic Informa  |                           | III-C-35             |

|         |   | 2 Loading TRIM   |                           | III-C-36             |

|         |   | 3 Initializing   |                           | III-C-36             |

|         |   | 4 Using TRIM I   |                           | III-C-37             |

|         | 4 |                  | truction Typeouts         | III-C-38             |

|         |   | 4.5.1 Set Ke     |                           | III-C-38             |

|         |   |                  | ify MTUS in A             | III-C-39<br>III-C-39 |

|         |   |                  | ify Tape Job in AL        | 111-C-39<br>111-C-39 |

|         |   | 4.5.4 Remove     | e Input Tape to Save      | 111-0-39             |

#### CHANGE 2

| Section | $\underline{\mathtt{Title}}$                                                     | <u>Page</u>        |

|---------|----------------------------------------------------------------------------------|--------------------|

|         | 4.5.5 Select Outputs in A 4.5.6 If Necessary Change Scratch Tapes for            | III-C-39           |

|         | This Output                                                                      | III-C-40           |

|         | 4.5.7 MTU ERROR CTXX Improve Condition                                           | III-C-40           |

|         | 4.5.8 Set Base Address in AL                                                     | III-C-40           |

|         | 4.5.9 NNNNN Duplicate Label XXXXXX                                               | III-C-40           |

|         | 4.5.10 Unallocated Tags nnnnn XXXXXX AAAAA                                       | III-C-41           |

|         | 4.5.11 TCS Error XX Table XX                                                     | III-C-41           |

|         | 4.5.12 Poly-Code Bank OFL                                                        | III-C-41           |

| IV      | Operator Service Routines                                                        | IV-1               |

| IV-A    | UPAK I Paper Tape Utility Package                                                | IV-A-1             |

|         | 1. General Information                                                           | IV-A-1             |

|         | 2. Program Description                                                           | I V-A-1            |

|         | 2.1 Paper Tape Load                                                              | IV-A-2             |

|         | 2.1.1 Load Absolute Typewriter Code                                              | IV-A-2             |

|         | 2.1.2 Load Absolute Bioctal Code                                                 | IV-A-3<br>IV-A-4   |

| •       | 2.1.3 Load Relocatable Bioctal Code 2.2 Paper Tape Absolute Typewriter Code Dump | IV-A-5             |

|         | 2.3 Paper Tape Absolute Bioctal Code Dump                                        | IV-A-5             |

|         | 2.4 Inspect and Change                                                           | IV-A-6             |

|         | 2.5 Store Constant in Memory                                                     | IV-A-6             |

|         | 2.6 Search Memory                                                                | IV-A-6             |

|         | 2.7 Copy Paper Tape                                                              | IV-A-7             |

|         | 2.8 Typewriter Dump                                                              | IV-A-7             |

|         | <ol><li>Loading and Operating Procedures</li></ol>                               | IV-A-8             |

|         | 3.1 Loading UPAK I                                                               | IV-A-8             |

|         | 3.2 Using UPAK I                                                                 | IV-A-9             |

|         | 3.2.1 Paper Tape Load                                                            | IV -A -9           |

|         | 3.2.2 Paper Tape Absolute Typewriter Code Du                                     | np IV-A-11         |

|         | 3.2.3 Paper Tape Absolute Bioctal Dump                                           | IV-A-11<br>IV-A-11 |

|         | 3.2.4 Inspect and Change                                                         | IV-A-11<br>IV-A-12 |

|         | 3.2.5 Store Constant in Memory 3.2.6 Search Memory                               | IV-A-12<br>IV-A-13 |

|         | 3.2.6 Search Memory<br>3.2.7 Copy Paper Tape                                     | IV-A-13            |

|         | 3.2.8 Typewriter Dump                                                            | IV-A-13            |

| III-B   | UPAK III Utility Package III                                                     | IV-B-1             |

|         | 1. General Information                                                           | IV-B-1             |

|         | 2. Control Program                                                               | IV-B-1             |

|         | 2.1 Program Description                                                          | IV-B-1             |

|         | 2.2 Loading UPAK III                                                             | IV-B-3             |

|         | 2.3 Expanding UPAK III                                                           | IV-B-5             |

| Section |    | <u>Title</u>                                                               | <u>Page</u>        |

|---------|----|----------------------------------------------------------------------------|--------------------|

|         | 3. | Paper Tape Handler Module (PTHAN) 3.1 Program Description                  | IV-B-6<br>IV-B-6   |

|         |    | 3.2 Operation Procedures                                                   | IV-B-9             |

|         |    | 3.2.1 Operation of Inspect and Change                                      | IV-B-9             |

|         |    | 3.2.2 Operation of Store Constant in Memory                                | IV-B-10            |

|         |    | 3.2.3 Manual Operation of all Paper Tape Loads                             | IV-B-10            |

|         |    | 3.2.4 Program Operation of All Paper Tape Loads                            |                    |

|         |    | 3.2.5 Manual Dump of Typewriter Code                                       | IV-B-11            |

|         |    | 3.2.6 Program Operation of Dump Typewriter Code                            |                    |

|         |    | 3.2.7 Manual Dump of Absolute Bioctal Code                                 | IV-B-11            |

|         |    | 3.2.8 Manual Operation of Dump Bioctal Code                                | IV-B-12            |

|         | 4. | Magnetic Tape Handler Module (UMTH)                                        | IV-B-12            |

|         |    | 4.1 Program Description                                                    | IV-B-12            |

|         |    | 4.2 Input Parameters                                                       | IV-B-12            |

|         |    | 4.3 Operating Procedures                                                   | IV-B-16            |

|         |    | 4.3.1 Operation Under Program Control                                      | IV-B-16            |

|         |    | 4.3.2 Manual Operation 4.4 Alarms and Status Indications                   | IV-B-16<br>IV-B-17 |

|         | 5. | 4.4 Alarms and Status Indications Magnetic Tape Duplication Module (MTDUP) | IV-B-18            |

|         | J. | 5.1 Program Description                                                    | IV-B-18            |

|         |    | 5.2 Input Parameters                                                       | IV-B-19            |

|         |    | 5.3 Operating Procedures                                                   | IV-B-21            |

|         |    | 5.3.1 Operation Under Program Control                                      | IV-B-21            |

|         |    | 5.3.2 Manual Operation                                                     | IV-B-21            |

|         |    | 5.4 Alarms and Status Indications                                          | IV-B-22            |

|         | 6. | TRIM III Output 10 Load Module (LOAD10)                                    | IV-B-22            |

|         |    | 6.1 Program Description                                                    | IV-B-22            |

|         |    | 6.2 Input Parameters                                                       | IV-B-24            |

|         |    | 6.3 Operating Procedures                                                   | IV-B-24            |

|         |    | 6.3.1 Operation Under Program Control                                      | IV-B-24            |

|         |    | 6.3.2 Manual Operation                                                     | IV-B-24            |

|         |    | 6.4 Alarms and Status Indications                                          | IV-B-25            |

|         | 7. | Inspect and Change and Store Constant Module                               | IV-B-25            |

|         |    | 7.1 Program Description                                                    | IV-B-25            |

|         |    | 7.2 Operating Procedure                                                    | IV-B-25            |

|         |    | 7.2.1 Inspect and Change                                                   | IV-B-25            |

|         |    | 7.2.2 Store Constant in Memory                                             | IV-B-26            |

|         | 8. | Print Memory Contents (PRINTC)                                             | IV-B-26<br>IV-B-26 |

|         |    | 8.1 Program Description                                                    | IV-B-20<br>IV-B-27 |

|         |    | 8.2 Operating Procedure                                                    | IV-B-27            |

|         |    | 8.2.1 Operation Under Program Control 8.2.2 Manual Operation               | IV-B-27            |

|         | 0  |                                                                            | IV-B-18            |

|         | 9. | Card Handler (DATCD) 9.1 Program Description                               | IV-B-28            |

|         |    | 9.1 Program Description 9.2 Input Parameters                               | IV-B-31            |

|         |    | 9.3 Operating Procedure                                                    | IV-B-31            |

|         |    | 9.4 Alarms                                                                 | IV-B-32            |

|         |    | / ♥ = - (1±1/(1111) €                                                      |                    |

| Section | <u>Title</u>                                                                           | <u>Page</u> |

|---------|----------------------------------------------------------------------------------------|-------------|

|         | <ol> <li>Printer Line Image on Tape and Tape-to-Printer<br/>Module (POTPOP)</li> </ol> | IV-B-3      |

|         | 10.1 Program Description                                                               | IV-B-3      |

|         | 10.2 Input Parameters                                                                  | IV-B-3      |

|         | 10.3 POT Operating Procedures                                                          | IV-B-3      |

|         | 10.3.1 Under Program Control                                                           | IV-B-3      |

|         | 10.3.2 Manual Operation                                                                | IV-B-3      |

|         | 10.4 POT Operating Procedures                                                          | IV-B-3      |

|         | 10.4.1 Under Program Control                                                           | IV-B-3      |

|         | 10.4.2 Manual Operation                                                                | IV-B-3      |

|         | 10.5 Alarms and Status Indicators                                                      | IV-B-3      |

|         | 11. Magnetic Tape Handler Module (JOSH)                                                | IV-B-3      |

|         | 11.1 Program Description                                                               | IV-B-3      |

|         | 11.2 Input Parameters                                                                  | IV-B-3      |

|         | 11.3 Operating Procedures                                                              | IV-B-3      |